Percobaan 1 No. 8

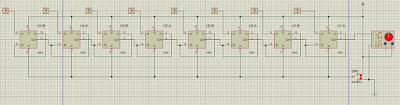

Buatlah rangkaian seperti gambar percobaan 1 dengan menggunkan D flip flop dan output 8 bit

Buatlah rangkaian seperti gambar percobaan 1 dengan menggunkan D flip flop dan output 8 bit

D flip-flop merupakan pengemangan dari RS flip-flop, pada D flip-flop kondisi output terlarang (tidak tentu) tidak lagi terjadi. D flip-flop merupakan dasar dari rangkaian utama sebuah memori penyimpan data digital. Input atau masukan pada RS flip-flop adalah 2 buah yaitu R (reset) dan S (set), kedua input tersebut dimodifikasi sehingga pada D flip-flop menjadi 1 buah input saja yaitu input atau masukan D (data) saja. Model modifikasi RS flip-flop menjadi D flip-flop adalah dengan penambahan gerbang NOT (Inverter) dari input S ke input R pada RS flip-flop.

Gambar diatas memperlihatkan D flip-flop yang dilengkapi dengan masukan enable/clock. Fungsi input enable/clock diatas adalah untuk menahan data masukan pada jalur Data (input D) agar tidak diteruskan ke rangkaian RS flip-flop. Prinsip kerja dari rangkaian Data flip-flop dengan clock diatas adalah sebagai berikut.

1. Apabila input clock berlogika 1 “High” maka input pada jalur data akan di teruskan ke rangkaian RS flip flop, dimana pada saat input jalur Data 1 “High” maka kondisi tersebut adalah Set Q menjadi 1 “High” dan pada saat jalur Data diberikan input 0 “Low” maka kondisi yang terjadi adala Reset Q menjadi 0 “Low”.

2. Kemudian Pada saat input Clock berlogika rendah maka data output pada jalur Q akan ditahan (memori 1 bit) walaupun logika pada jalur input Data berubah. Kondisi inilah yang disebut sebagai dasar dari memor 1 bit. Untuk lebih jelasnya dapat dilihat pada tabel Data flip-flop berikut.

Pada saat clock '1', Nilai output Q akan sama dengan Input D, pada awal permulaan rangkaian aktif, maka D '0' sehingga Q '0', Q- '1'. Nilai Q- ini terhubung ke input D pada D flip flopnya sendiri dan input CLK pada D flip flop sebelahnya. Sehingga pada saat Q- bernilai '1' maka akan mengclock D flip flop di sebelahnya.

Pada saat clock '0' maka sesuai dengan tabel kebenarannya dia akan mempertahankan kondisi sebelumnya.

Rangkaian ini input yang masuk secara beurutan atau satu persatu. Input digeser ke flip-flop disampingnya sesuai gerak dari clock. Rangkaian asynchronous counter ini akan terlihat pergerakan dari output Q nya seperti perhitungan biner 8 bit. Yaitu yang artinya perhitungan desimal dari 0 hingga 255. Jika sudah 11111111 dia akan kembali lagi menjadi 00000000 dan melakukan perhitungan seperti tadi kembali. Pada D flip flop IC 7474 ini juga terdapat reset dimana dia aktif rendah sehingga jika dihubungkan ke ground dia akan melakukan reset dan menjadi 00000000.

Tidak ada komentar:

Posting Komentar