5.10 Guidelines to using TTL Devices

- Mengetahui apa itu transistor transistor logic (TTL)

- Mengetahui cara membuat rangkaian transistor transistor logic (TTL)

1. Transistor

2. Resistor

Resistor atau hambatan adalah salah satu komponen elektronika yang memiliki nilai hambatan tertentu, dimana hambatan ini akan menghambat arus listrik yang mengalir melaluinya.

Transistor Transistor Logic (TTL) adalah keluarga logika yang diimplementasikan dengan teknologi proses bipolar yang menggabungkan atau mengintegrasikan transistor NPN, dioda persimpangan PN dan difusi resistor dalam struktur monolitik tunggal untuk mendapatkan fungsi logika yang diinginkan. Gerbang NAND adalah blok bangunan dasar keluarga logika ini.

Subfamili yang berbeda dalam keluarga logika ini, seperti yang diuraikan sebelumnya,termasuk TTL standar, TTL daya rendah, TTL daya tinggi, Schottky TTL daya rendah, Schottky TTL, lanjutan Schottky TTL daya rendah, TTL Schottky canggih dan TTL cepat. Dalam paragraf berikut, kami akan menjelaskan secara singkat masing-masing subfamili ini dalam hal struktur dan karakteristik internal parameter.

Operasi Sirkuit

Operasi Sirkuit

Ketika kedua input berada dalam keadaan logika TINGGI seperti yang ditentukan oleh keluarga TTL (VIH = 2 V minimum), arus mengalir melalui basis-collector PN junction diode dari transistor Q1 ke dalam basis transistor Q2. Transistor Q2 dihidupkan ke saturasi, dengan hasil bahwa transistor Q3 dimatikan dan transistor Q4 AKTIF. Ini menghasilkan RENDAH logika pada output, dengan VOL maksimum 0,4 V ketika sedang tenggelam arus 16 mA dari beban eksternal diwakili oleh input dari fungsi logika didorong oleh output. Tindakan tenggelam saat ini ditunjukkan pada Gambar 5.7 (a). Transistor Q4 juga disebut sebagai transistor saat ini tenggelam atau pull-down, untuk alasan yang jelas. Diode D1 digunakan untuk mencegah transistor Q3 dari melakukan bahkan sejumlah kecil arus ketika output RENDAH.

Ketika outputnya RENDAH, Q4 dalam saturasi dan Q3 akan melakukan sedikit dalam ketiadaan D1. Juga input arus IIH dalam keadaan TINGGI tidak lain adalah arus bocor dioda sambungan terbalik dan biasanya 40 A. Ketika salah satu dari dua input atau kedua input berada dalam keadaan logika RENDAH, basis-emitor wilayah Q1 melakukan arus, mendorong Q2 untuk memotong dalam proses. Ketika Q2 dalam keadaan cut-off, Q3 didorong untuk konduksi dan Q4 untuk cut-off. Ini menghasilkan output TINGGI logika dengan VOH (min.) = 2,4 V dijamin untuk tegangan suplai minimum VCC dan sumber arus 400 A.

Tindakan sumber saat ini ditampilkan pada Gambar 5.7 (b). Transistor Q3 juga disebut sebagai sumber arus atau transistor pull-up. Juga IIL arus input level rendah, diberikan oleh (VCC −VBE1 / R1, adalah 1,6 mA (maks.) Untuk VCC maksimum.

NOT Gate (or Inverter)

Gambar 5.8 menunjukkan skema internal gerbang NOT (inverter) dalam keluarga TTL standar. Itu Skema yang ditunjukkan adalah salah satu dari enam inverter dalam hex inverter (tipe 7404/5404). Internal skematis sama dengan gerbang NAND kecuali bahwa transistor input adalah tunggal normal Transistor NPN alih-alih multi-emitor.

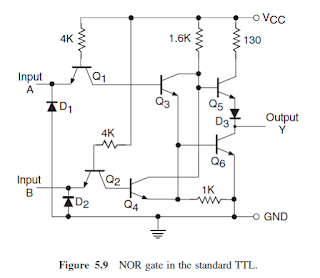

Gerbang NOR

Gambar 5.9 menunjukkan skema internal gerbang NOR dalam keluarga TTL standar. Skematis yang ditunjukkan adalah salah satu dari empat gerbang NOR di quad dua input gerbang NOR (tipe 7402/5402). Di sisi input ada dua transistor terpisah, bukan transistor multi-emitor dari gerbang NAND. Masukan dimasukkan ke penghasil dua transistor, pengumpul yang lagi memberi makan basis transistor dengan kolektor dan terminal emitor mereka diikat bersama. Nilai resistansi yang digunakan sama dengan yang digunakan dalam kasus gerbang NAND. Tahap output juga merupakan tiang totem yang sama tahap output. Sirkuit ini cukup jelas. Satu-satunya kondisi input dimana transistor Q3 dan Q4 tetap dalam cut-off, sehingga mendorong Q6 ke cut-off dan Q5 ke konduksi, adalah ketika kedua input berada dalam keadaan logika RENDAH. Output dalam kasus seperti ini adalah logika TINGGI. Untuk semua kondisi input lainnya, baik Q3 atau Q4 akan melakukan, mendorong Q6 ke saturasi dan Q5 untuk memotong, menghasilkan logika RENDAH di hasil.

OR Gate

Gambar 5.11 menunjukkan skema internal gerbang OR dalam keluarga TTL standar. Skema yang ditampilkan adalah salah satu dari empat gerbang OR di quad OR-input gerbang dua (tipe 7432/5432). Kami akan mulai dengan menyelidiki kondisi input yang akan menghasilkan output RENDAH. Output RENDAH menuntut Q8 jenuh dan Q7 cut-off. Ini pada gilirannya mengharuskan Q6 berada dalam saturasi dan Q5, Q4 dan Q3 berada dalam cut-off. Ini hanya mungkin ketika Q1 dan Q2 berada dalam saturasi. Artinya, kedua input berada dalam keadaan logika RENDAH. Ini memverifikasi salah satu entri dari tabel kebenaran gerbang OR. Sekarang mari kita lihat apa yang terjadi ketika salah satu dari dua input didorong ke status TINGGI. Ini mendorong salah satu dari dua transistor Q3 dan Q4 ke saturasi, yang memaksa Q5 untuk saturasi dan Q6 untuk terputus. Ini mendorong Q7 ke konduksi dan Q8 untuk memotong, menghasilkan logika output TINGGI.

Pedoman berikut harus dipatuhi saat menggunakan perangkat keluarga TTL:

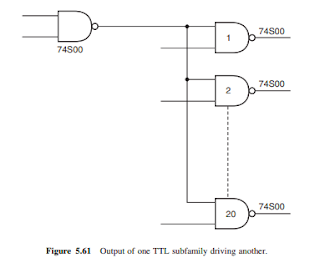

1. Mengganti IC TTL dari satu subfamily TTL dengan yang lain milik subfamily lain (the

ketik nomor yang tetap sama) tidak boleh dilakukan secara membabi buta. Perancang harus memastikan bahwa perangkat pengganti kompatibel dengan sirkuit yang ada sehubungan dengan parameter tersebut

sebagai kemampuan drive output, pemuatan input, kecepatan dan sebagainya. Sebagai ilustrasi, mari kita asumsikan itu

kami menggunakan 74S00 (quad dua input NAND), output yang mendorong 20 NAND berbeda

input diimplementasikan menggunakan 74S00, seperti yang ditunjukkan pada Gambar 5.61. Sirkuit ini berfungsi dengan baik seperti Schottky

Keluarga TTL memiliki fan-out 20 dengan output kemampuan drive TINGGI 1 mA dan input

Persyaratan TINGGI saat ini 50 A. Jika kita mencoba mengganti driver 74S00 dengan driver 74LS00,

sirkuit gagal berfungsi karena NAND 74LS00 memiliki kemampuan drive TINGGI keluaran 0,4 mA

hanya. Itu tidak bisa memberi makan 20 beban input NAND diimplementasikan menggunakan 74S00. Dengan melakukan itu, kita akan menjadi

melebihi kemampuan fan-out kondisi-TINGGI pada perangkat. Juga, 74LS00 memiliki spesifikasi arus keluaran 8 mA, sedangkan persyaratan arus tenggelam dari 74S00 adalah 2 mA.

Ini menyiratkan bahwa 74LS00 hanya dapat memberi makan empat input 74S00 dalam kondisi RENDAH. Dengan makan

sebanyak 20 input, kita akan melebihi kemampuan fan-out LOW-state 74LS00 secara besar-besaran

batas.

2. Tidak ada input dan output IC TTL yang harus didorong oleh lebih dari 0,5 V di bawah tanah

referensi.

3. Teknik pentanahan yang tepat harus digunakan saat merancang tata letak PCB. Jika landasannya

tidak benar, arus ground loop menimbulkan penurunan voltase, dengan hasil IC yang berbeda

tidak pada referensi yang sama. Ini secara efektif mengurangi kekebalan kebisingan.

4. Rel catu daya harus selalu dipisahkan dengan benar dengan kapasitor yang sesuai sehingga ada

tidak ada penurunan pada VCC rail karena input dan output membuat transisi logika. Biasanya dua kapasitor

digunakan pada titik VCC setiap IC. Disk keramik 0,1 F harus digunakan untuk merawat

kebisingan frekuensi tinggi, sedangkan elektrolitik 10-20 F cukup baik untuk menghilangkan variasi frekuensi rendah yang dihasilkan dari variasi arus ICC yang diambil dari VCC, tergantung pada logika

keadaan input dan output. Agar efektif, kapasitor decoupling harus dipasang sedekat mungkin

layak untuk pin VCC dari IC.

5. Input yang tidak digunakan tidak boleh dibiarkan mengambang. Semua input yang tidak digunakan harus dikaitkan dengan logika HIGH in

kasus gerbang AND dan NAND, dan untuk ground dalam kasus gerbang OR dan NOR. Sebuah alternatif

adalah menghubungkan input yang tidak digunakan ke salah satu input yang digunakan.

6. Saat menggunakan perangkat kolektor terbuka, pull-up resistif harus digunakan. Nilai resistensi pull-up

harus ditentukan dari persamaan berikut:

RX = VCC maks −VOL / IOL −N2 RENDAH × 1 6 (5.11)

RX maks = VCC min −VOH / N1 × IOH + N2 TINGGI × 40 (5.12)

di mana RX adalah resistor pull-up eksternal; RX (maks.) Adalah nilai maksimum dari pull-up eksternal

penghambat; N1 adalah jumlah output WIRED-OR; N2 adalah jumlah beban input unit yang sedang

didorong; IOH adalah output arus bocor TINGGI (dalam mA); IOL adalah arus keluaran level RENDAH dari

elemen penggerak (dalam mA); VOL adalah tegangan output level RENDAH; dan VOH adalah tingkat TINGGI

tegangan output. Satu beban unit TTL dalam status TINGGI = 40 mA, dan satu beban unit TTL dalam

Status RENDAH = 1,6 mA.

Prinsip kerja :

Rangkaian diatas merupakan salah satu panduan menggunakan peranfkat TTL, rangkaian tersebut menggunakan beberapa gerbang Nand untuk menjalankan logika dari TTL. input pada gerbang logika akan berpengaruh terhadap outputnya. input dan output pada gerbang logika akan bekerja sesuai tabel kebenaran gerbang logika tersebut yang dapat dilihat pada teori diatas.

5.video [kembali]

Download HTML Rangkaian KLIK DISINI !!!!!

Download Simulasi Rangkaian KLIK DISINI !!!!!

Download Video Simulasi Rangkaian KLIK DISINI !!!!!

Download Simulasi Rangkaian KLIK DISINI !!!!!

Download Video Simulasi Rangkaian KLIK DISINI !!!!!

Tidak ada komentar:

Posting Komentar