1. Tujuan

- Mengetahui pengertian J-K Flip-flop

- Mengetahui logika penggunaan J-K Flip-flop

2. Alat dan Bahan

1. IC 7410

IC 74HC10/7410 digunakan dalam rangkaian ini sebagai gerbang Nand yang membuktikan cara kerja dari rangkaian J-K Flip-flop. Ic ini memiliki 3 input yang dipakai dalam rangkaian tersebut.

2. IC 7420

IC 7420 digunakan dalam rangkaian ini sebagai gerbang Nand yang membuktikan cara kerja dari rangkaian J-K Flip-flop. Ic ini memiliki 4 input yang dipakai dalam rangkaian tersebut.

3. Logicstate

4. Logicprobe

3. Teori

J-K Flip-Flop

J-K

flip-flop berperilaku dengan cara yang sama seperti flip-flop R-S kecuali untuk

salah satu entri dalam tabel fungsi. Dalam kasus flip-flop RS, kombinasi input

S = R = 1 (dalam kasus flip-flop dengan input HIGH aktif) dan kombinasi input S

= R = 0 (dalam kasus flip-flop dengan input RENDAH aktif) dilarang. Dalam kasus

flip-flop J-K dengan input HIGH aktif, output dari flip-flop beralih, yaitu, ia

pergi ke keadaan lain, untuk J = K = 1. Output beralih untuk J = K = 0 dalam

kasus flip-flop yang memiliki input RENDAH aktif. Dengan demikian, flip-flop

J-K mengatasi masalah kombinasi input terlarang dari flip-flop R-S. Gambar

10.26 (a) dan (b) masing-masing menunjukkan simbol rangkaian flip-flop J-K yang

dipicu level dengan input HIGH dan active RENDAH aktif, bersama dengan tabel

fungsinya. Gambar 10.27 menunjukkan realisasi flip-flop J-K dengan flip-flop

R-S.

Tabel karakteristik untuk JK flip-flop dengan input HIGH J dan K yang aktif

dan JK flip-flop dengan input L J dan K yang aktif ditunjukkan masing-masing

dalam Gambar 10.28 (a) dan (b) Peta Karnaugh yang sesuai ditunjukkan pada

Gambar 10.28 (c) untuk tabel karakteristik Gambar 10.28 (a) dan Gambar 10.28

(d) untuk tabel karakteristik Gambar 10.28 (b). Persamaan karakteristik untuk

peta Karnaugh dari Gambar 10.28 (c) dan (d) masing-masing.

10.5.1 J-K Flip-Flop

dengan Input PRESET dan CLEAR

Seringkali diperlukan untuk menghapus flip-flop ke keadaan logika ‘0’ (Qn =

0) atau mengaturnya ke keadaan logika ‘1’ (Qn = 1). Contoh bagaimana hal ini

diwujudkan ditunjukkan pada Gambar 10.29 (a). Flip-flop dihapus (yaitu, Qn = 0)

setiap kali input CLEAR adalah '0' dan input PRESET adalah '1'. Flip-flop

diatur ke keadaan logika '1' kapan pun input PRESET adalah '0' dan input CLEAR

adalah '1'. Di sini, input CLEAR dan PRESET aktif saat RENDAH. Gambar 10.29 (b)

menunjukkan simbol sirkuit dari flip-flop J-K yang dapat diatur, dapat dihapus

ini. Gambar 10.29 (c) menunjukkan tabel fungsi flip-flop tersebut. Jelas dari

tabel fungsi bahwa, setiap kali input PRESET aktif, output akan menuju ke

status '1' terlepas dari status input jam, J dan K. Demikian pula, ketika

flip-flop dihapus, yaitu, input CLEAR aktif, output masuk ke status '0'

terlepas dari status input jam, J dan K. Dalam flip-flop jenis ini, input

PRESET dan CLEAR tidak boleh diaktifkan secara bersamaan.

10.5.2 Master-Slave

Flip-Flops

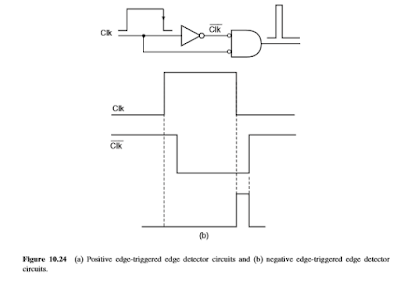

Setiap kali lebar pulsa

clocking flip-flop lebih besar dari penundaan propagasi flip-flop, perubahan

status pada output tidak dapat diandalkan. Dalam kasus flip-flop yang dipicu

tepi, lebar pulsa ini akan menjadi lebar pulsa pemicu yang dihasilkan oleh

bagian detektor tepi flip-flop

dan bukan lebar pulsa sinyal jam input.

Fenomena ini disebut sebagai masalah balapan. Karena penundaan propagasi

biasanya sangat kecil, kemungkinan terjadinya kondisi lomba cukup tinggi. Salah

satu cara untuk mengatasi masalah ini adalah dengan menggunakan konfigurasi

master-slave. Gambar 10.30 (a) menunjukkan flip-flop master-slave yang dibangun

dengan dua flip-flop J-K. Flip-flop pertama disebut master flip-flop dan yang

kedua disebut slave. Jam untuk flip-flop budak adalah pelengkap dari jam ke

flip-flop utama. Ketika pulsa jam hadir, master flip-flop diaktifkan saat slave

flip-flop dinonaktifkan. Akibatnya, master flip-flop dapat mengubah status

sementara slave flip-flop tidak bisa. Ketika jam berjalan RENDAH, master

flip-flop dinonaktifkan sementara slop flip-flop diaktifkan. Oleh karena itu,

slave J-K flip-flop berubah status sesuai status logika pada input J dan K-nya.

Karena itu isi master flip-flop ditransfer ke flip-flop slave, dan master

flip-flop, yang dinonaktifkan, dapat memperoleh input baru tanpa mempengaruhi

output. Seperti yang akan jelas dari uraian di atas, flip flop master-slave

adalah flip-flop yang dipicu pulsa dan bukan yang dipicu oleh tepi. Gambar

10.30 (b) memperlihatkan tabel kebenaran dari flip-flop J-K master-slave dengan

input PRESET RENDAH dan CLEAR aktif dan input J dan K HIGH T aktif. Konfigurasi

master-slave menjadi usang. Teknologi IC terbaru seperti 74LS, 74AS, 74ALS,

74HCand74HCTdonothavemaster-slaveflip-flopsintheir seri.

Prinsip Kerja :

Pada gambar diatas, merupakan gambar simulasi dari J-K Flip-flop, dimana rangkaian tersebut terdapat di dalam IC J-K Flipflop yang bekerja menurut logika pada tabel diatas. ketika salah satu kaki Preset dan Clear ada yang berlogika 0 maka input dari J-K akan diabaikan. Namun jika kedua input Preset dan Cleat berlogika 1 maka input pada J-K akan berpengaruh terhadap output dari rangkaian tersebut berdasarkan logika pada tabel.

6. Link Download

Tidak ada komentar:

Posting Komentar